ISSN (Print) 2313-4410, ISSN (Online) 2313-4402

© Global Society of Scientific Research and Researchers

ttp://asrjetsjournal.org

# Harmonic Distortion Reduction using Seven level H-Bridge VSI Topology based Dynamic Voltage Restorer

Ir. Dr K Chandrasekaran<sup>\*</sup>

Assistant Professor, University Tunku Abdul Rahman, Kampar. Malaysia, Contact no. 019-5584754 Email: kchandra@utar.edu.my

#### Abstract

This paper demos the model, the control and simulation of H-Bridge VSI topology based Dynamic Voltage Restorer (DVR). The structure and the operating principle of the Cascaded H-Bridge Seven level Inverter is realized. The phase shifted SPWM was adapted to reduce the lower order harmonics of the output voltage. The controller was based on the dqo transformation. The performance of the proposed method was ascertained in PSCAD. The simulation results are appraised and discussed. The controller was able to manage the zero-sequence voltage during unbalance fault period. The phase shift SPWM was incorporated with low frequency and subsequently, the switching loss was low. The Total Harmonic Distortion (THD) with the designed DVR was significantly low in comparison to other traditional models and was within the IEEE Standards 519-2014. The envisioned controller algorithm provides excellent voltage improvements.

*Keywords:* DVR; Phase shifted Pulse width modulation (PSPWM); Voltage source inverter (VSI); Voltage harmonics; Voltage sag.

## 1. Introduction

Voltage sag is the most common power quality problem in an electrical network. Voltage sag is a short duration (10 ms to 1 minute) event where there is a reduction in r.m.s voltage magnitude across the load. The two vital parameters are sag magnitude and duration. The voltage sag ranges from 10 % to 90 % of nominal voltage (which corresponds to 90 % to 10 % remaining voltage) with a duration from half a cycle to 1 min. Voltage sag is due to a fault in the utility system, a fault at the customer's end or a starting a large motor or transformer energizing.

-----

<sup>\*</sup> Corresponding author.

The most common faults are single-phase faults account to 80 %, followed with two phases fault and two phases fault to ground. Large fault current results in a voltage drop across the network impedance. The voltage in the faulted phases drops close to zero. A voltage swell condition occurs when the voltage of one or more phase rises above the specified tolerance for a short period of time. Harmonics distortion is due to nonlinear loads. The main advantage of multilevel inverters is that the output voltage can be generated with low harmonics. The harmonics decrease proportionately to the inverter level. There are numerous types of multilevel inverters: cascaded H-bridge (CHB), neutral point clamped, flying capacitor. The CHB inverters are being widely used because of their modularity and simplicity. Various modulation methods can be applied to CHB inverters. CHB inverters can increase the number of output voltage levels by increasing the number of H-bridges. Hence, voltage imperfections in the network cannot be tolerated for most industrial applications due to down time and production losses. Thus, this motivated to develop a simple innovative hybrid DVR to cater for the voltage imperfections in the 400 Volts network. This paper demos a new Hybrid DVR with a dqo controller based CHB multilevel inverter for the harmonics and voltage sag and voltage harmonics mitigation. The advantages of this arrangement, the voltage levels can be increased, low switching losses, hybrid filters and higher order harmonic elimination. This Hybrid DVR is cost effective alternative compared with other commercially available custom power devices and can be used in both the industrial as well as academic purposes.

# 1.1 Objectives

- i. Develop an innovative Hybrid DVR model to mitigate the voltage imperfections in a 400 Volts distribution network.

- ii. Investigate the unique dqo transformation controllers.

## 2. Literature Review

Many researchers have proposed [1,2] voltage sag mitigation and voltage harmonics compensation methods independently by using series active power filter and tuned shunt passive LC filters as a hybrid integrated model. The proposed control scheme in [3] is effective in compensating voltage sag and harmonics when a bank of tuned shunt passive LC filters connected at the load end are used along with a series active filter. In this case, the series active power filter improves the harmonic filtering characteristic of shunt passive LC filter. The LC harmonic filter will divert the load current harmonics to the ground, thus preventing the voltage waveform distortion at the point of common coupling (PCC). However, the improvement in THD level of voltage at the load end is not clearly established. The control scheme in [1] is based on the d-q algorithm. The main drawback here is the use of tuned shunt passive LC filters for current harmonics filtering which either trap or block the harmonic currents from returning to the source. Since the passive filters needs to be tuned to the specific harmonics, the line impedance must be known. Furthermore, a passive harmonic filter may excite system oscillations. Two delay units used to generate balanced 3-phase voltages for d-q transformation in the proposed controller might result in slow response. The controller is not tested for different types of faults such as balanced and unbalanced faults, balanced and unbalanced faults with harmonics generating loads, as well as harmonics alone. Also, the simulation results in various faults that are not presented or discussed.

This research proposes an innovative controller based on the Synchronous Rotating Reference Frame (SRRF) enabling the DVR to operate in the unbalanced and distorted supply conditions. With the improved scheme, the proposed DVR model will be able to achieve an improved voltage swell and sag mitigation as well as compensation of voltage harmonics, subsequently with a low THD level. This research project can provide better results in terms of the THD level and simplicity as compared to the conventional model explained in the literature. This would provide valuable input to the academics and solutions on power quality improvements to the industrial and the commercial sectors.

# 3. Modelling of DVR

# 3.1 Principle of DVR

The objective of the control system is to manage the load voltage during supply system voltage disturbances. The controller is to detect the voltage imperfections such as voltage sag, swell, and voltage harmonics and inject voltage deviation by providing appropriate switching strategies for the inverter. A constant magnitude load voltage is maintained by the proposed controller under the balanced and unbalanced dynamic power quality disturbances.

The control strategy of DVR should satisfy the following criterions:

- Reliable and fast response for both the transient states and steady states.

- Compensation for various types of sags and for different load connection.

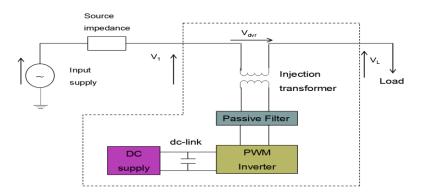

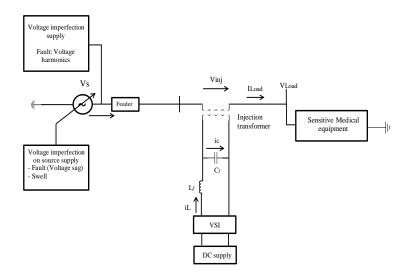

Robustness for nonlinear load conditions, sudden load changes and system parameter variations. The DVR is shown in Figure 3.0. Features consists of an injection transformer whose primary is connected in series with the supply line, a PWM-VSI which is connected in series with the secondary side of injection transformer, dc supply, and a passive filter. The dc-link with a constant voltage across the capacitor provides the active and reactive power during the voltage sag.

Figure 3.0: Schematic diagram of DVR

## 3.2 Control design

## 3.2.1 Synchronous rotating reference frame (SRRF) controller algorithm

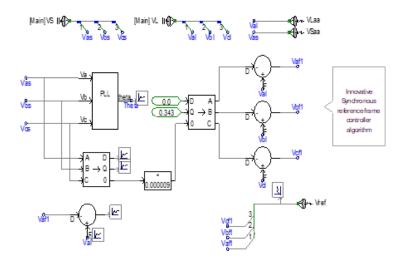

In the d-q based controller algorithms, the measured system voltage will be transferred into Stationary Reference Frame using Clarke transformation, and then transferred into Synchronous Rotating Frame using Park transformation. The reference compensation voltages to control DVR are generated by comparing the calculated desired system voltages and the measured load side voltages. The error signals are subjected to a phase shift multicarrier SPWM controller to determine the desired switching pattern for the IGBTs of DVR. The developed innovative SRRF controller is simplicity to implement, required minimum components and fast response. The innovative control strategy is shown in Figure 3.1. The input supply voltage (Vas, Vbs, Vcs) contains both the fundamental as well as the distorted components. Since, the supply voltage is distorted, a phase locked loop (PLL) is used to achieve synchronization with the supply voltage. The error signals are Vaf1, Vbf1, Vcf1.

Figure 3.1: Synchronous reference frame controller algorithm.

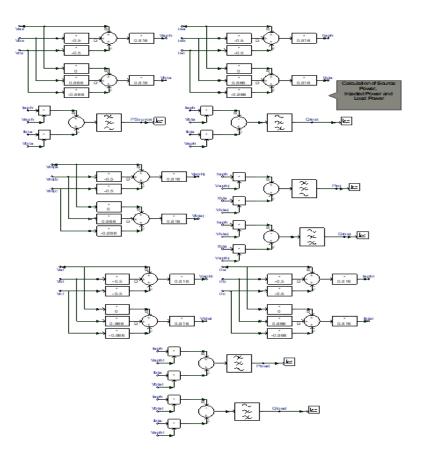

# 3.2.2 Control scheme for power measurement

A simple and efficient control scheme has been designed for the various power measurements as shown in Figure 3.2. This control is based on the Clarkes transformation theory.

Figure 3.2: Mathematical based control scheme for power measurement

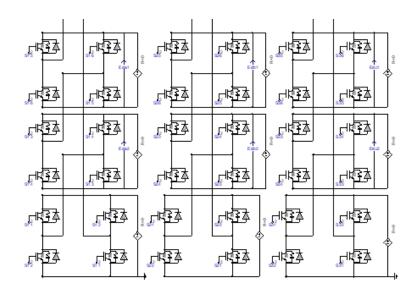

# 3.2.3 PSCAD implementation of cascaded H-BRIDGE multilevel inverter

The approach used in [3,4,5,6] to implement the cascaded H-BRIDGE multilevel inverter is described. The PSCAD model of the three-phase inverter for the DVR system is shown in Figure 3.3. The converter topology is based on the series connection of single-phase inverters with separate dc sources. The structure of separate dc sources is well suited for various renewable energy sources such as fuel cell, photovoltaic. Each phase has three series connected H-bridge cell. Each cell will have four power switches with anti-parallel diodes and dc power supply. The CHB inverter in Figure 3.3 can produce phase voltages with seven voltage levels. There are six carrier signals. Three of them are applied across the positive half cycle of the modulating signal. The remaining three of them are applied across the negative half cycle of a leg. Same way the pulses are generated for next two phases. From Figure 3.3, when the switches S15, S15, S13, S13 and S11, S11 conducts, the output voltage of the H-bridge cells c1, c2 and c3 is Vc1 = Vc2 = Vc3 = E = Vdc, and the resultant phase voltage of the voltages generated by the different cells. In similar fashion, when switches S16, S16, S14, S14 and S12, S12 is switched on, the output voltage is Van = -3E = -3Vdc. The remaining three voltage levels are +Vdc, +2Vdc, 0, and -Vdc, -2Vdc responding to the various switching states are exhibited in Table 3.0.

Figure 3.3: The PSCAD model of the three-phase inverter for the DVR system

# Table 3

| Volt  | Switching states |     |     |     |     |      |     |     |      |     |      |     |

|-------|------------------|-----|-----|-----|-----|------|-----|-----|------|-----|------|-----|

|       | S15              | S15 | S16 | S16 | S13 | \$13 | S14 | S14 | \$11 | S11 | \$12 | S12 |

| +Vdc  | 1                | 1   | 0   | 0   | 0   | 1    | 0   | 1   | 0    | 1   | 0    | 1   |

| +2Vdc | 1                | 1   | 0   | 0   | 1   | 1    | 0   | 0   | 0    | 1   | 0    | 1   |

| +3Vdc | 1                | 1   | 0   | 0   | 1   | 1    | 0   | 0   | 1    | 1   | 0    | 0   |

| 0     | 0                | 1   | 0   | 1   | 0   | 1    | 0   | 1   | 0    | 1   | 0    | 1   |

| -Vdc  | 0                | 0   | 1   | 1   | 0   | 1    | 0   | 1   | 0    | 1   | 0    | 1   |

| -2Vdc | 0                | 0   | 1   | 1   | 0   | 0    | 1   | 1   | 0    | 1   | 0    | 1   |

| -3Vdc | 0                | 0   | 1   | 1   | 0   | 0    | 1   | 1   | 0    | 0   | 1    | 1   |

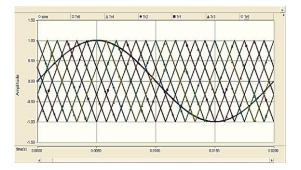

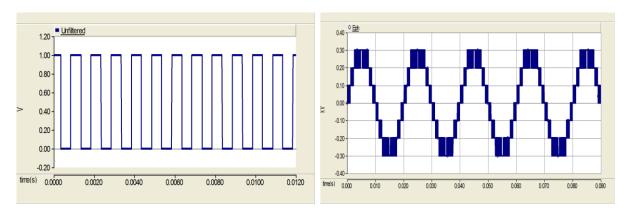

The Phase Shifted Carrier SPWM is displayed in Figure 3.4. The unfiltered set of pulses generated by the inverter for phase A is as shown in Figure 3.5. The single-phase output voltage is displayed in Figure 3.6. The interface of the control signal and the triangular signal will boost the number of pulses per cycle and ultimately minimize the lower order harmonics [7].

Figure 3.4: The Phase Shifted Carrier SPWM

Figure 3.5: Phase A PWM Output Pulses

Figure 3.6: The single-phase output voltage 7-level multilevel inverter.

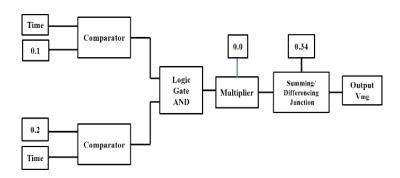

3.2.4 Proposed seven level control circuit.

Figure 3.7: Single pole pulse generation circuit in PSCAD

The phase shift between any two adjacent carrier waves as expressed by Equation 3.0.

The PWM signals for controlling the IGBTs of m-level multilevel converter will be generated when comparing the modulating wave with the carrier waves. The pulse generation circuit is shown in Figure 3.7. For the triangular wave, the frequency is set at 4650 Hz, and the duty cycle is 50 %, maximum and minimum output level is +1 and -1, respectively for optimum operation and to minimize the harmonics. The pulse generation is crucial to initiate the VSI gate switches. The appropriate pulse pattern is needed to generate the appropriate 7level output staircase waveform. The reference signal wave is compared with the six triangular carriers of same frequency and magnitude generated from the phase shift technique. When the reference signal surpasses the carrier, instant pulses are synthesized to prompt the switch to the 0N state. As illustrated in Figure 3.7, six triangular carrier waves are required with а 60 degrees phase displacement between any two adjacent carriers [8,9,10].

# 3.2.5 Simulation of Seven Level Cascade Inverter

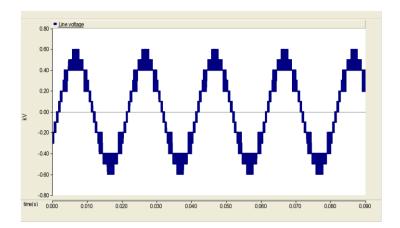

The 7-level inverter has six carrier signals. From these signals twelve PWM signals are generated and sent to the twelve switches of a leg. Equally the pulses are triggered for the next two phases. The modulating signal is phase shifted by 60 degrees. The maximum output line voltage of 7-level cascaded inverter is 600 Volts, as shown in Figure 3.8.

Figure 3.8: Line voltage of 7-level cascaded inverter

# 3.2.6 Harmonics compensation

In the steady-state conditions, the harmonic currents generated by the main nonlinear load will cause a voltage drop across system impedance and distort the supply voltage,  $V_s$  and the voltage at the sensitive load, VLoad as shown in Figure 3.9.

Figure 3.9: Single line diagram to represent power quality problem.

The voltage at the load VLoad consists of the fundamental and the harmonic voltage components. In Figure 3.9, distorted voltage  $V_S$  will appear on the upstream source-side of the sensitive load and the phase voltages can be expressed as

$$V_{\rm sa} = \sum_{n=1}^{\infty} \begin{bmatrix} V_{\rm on} + V_{1n} \sin(n\omega_0 t + \varphi_{1n}) \\ + V_{2n} \sin(n\omega_0 t + \varphi_{2n}) \end{bmatrix}$$

(Equation 3.1)

$$V_{\rm sb} = \sum_{n=1}^{\infty} \begin{bmatrix} V_{\rm on} + V_{1n} \sin\left(n\omega_0 t + \varphi_{1n} - 2n\frac{\pi}{3}\right) \\ + V_{2n} \sin(n\omega_0 t + \varphi_{2n} + 2n\frac{\pi}{3}) \end{bmatrix}$$

(Equation 3.2)

$$V_{\rm sc} = \sum_{n=1}^{\infty} \begin{bmatrix} V_{\rm on} + V_{1n} \sin\left(n\omega_0 t + \varphi_{1n} + 2n\frac{\pi}{3}\right) \\ + V_{2n} \sin(n\omega_0 t + \varphi_{2n} - 2n\frac{\pi}{3}) \end{bmatrix}$$

(Equation 3.3)

$V_{\rm on}$  is zero phase sequence voltage component.

$V_{1n}$  and  $\varphi_{1n}$  are magnitude and phase of positive sequence voltage component.

$V_{2n}$  and  $\varphi_{2n}$  are magnitude and phase of negative sequence voltage component.

The distorted voltage at the sensitive load end is undesirable. The desirable voltage  $V_L$  at the sensitive load comprises the fundamental components as Equation (3.1) - (3.3).

$$V_{La}^{`} = V_{11} \sin(\omega_0 t + \varphi_{11})$$

(Equation 3.4)

$$V_{Lb}^{`} = V_{11} \sin(\omega_0 t - 2\frac{\pi}{3} + \varphi_{11})$$

(Equation 3.5)

$$\dot{V}_{Lc} = V_{11} \sin(\omega_0 t + 2\frac{\pi}{3} + \varphi_{11})$$

(Equation 3.6)

The voltage that is injected by the DVR will compensate for the difference between  $V_s$  and the desired voltage VLoad described by Equation (3.4) - (3.6). The injected voltage by the DVR will contain both the ac voltage component in series with the distorted supply voltage  $V_s$  and contains the entire harmonic component as Equation (3.1) - (3.3). Equation (3.1) - (3.3) express in compact expression:

$$\vec{V}_{s} = [V_{sa}, V_{sb}, V_{sc}]^{T}$$

and Equation (3.4) - (3.6) denoted by  $\vec{V}_{Lf} = [V_{La}, V_{Lb}, V_{Lc}]$

Let  $V_{Lh}$  be the vector containing all the harmonic components in Equation (3.1) - (3.3).

Hence from Equation (3.1) - (3.3), the injection voltage V<sub>inj</sub> from the DVR to compensate would have to be

$$V_{inj} = -V_{Lh} = V_{Lf} - V_{Load}$$

(Equation 3.7)

$V_{Lf}$  is the fundamental voltage component. The injection voltage  $V_{inj}$  that is generated will be used to mitigate the harmonic distortions. From Figure 3.9,  $L_f$  filters the high-frequency harmonic voltage components. Low order harmonics (5<sup>th</sup>, 7<sup>th</sup>, 11<sup>th</sup> and 13<sup>th</sup>) are due to the nonlinearity between the IGBTs in the same leg, the voltage drop during the on-state of IGBTs and also distortion in the supply voltage [11,12,13,14].

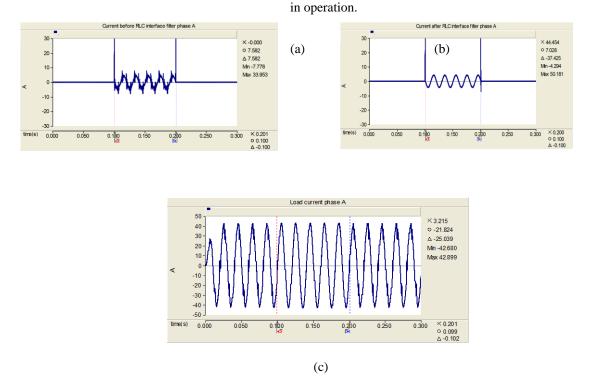

Figure 3.10(a) represents the injected current phase A before the RLC interface filter. This current is distorted. Figure 3.10(b) represents the injected current phase A after the RLC interface filter. Between the intervals 0.1 to 0.2 sec, the current is minimum distortion less. Figure 3.10(c) represents the load current phase A with the DVR

Figure 3.10: Injected current Phase A

(a) before RLC interface filter

(b) after RLC interface filter

(c) load current Phase A

# 3.2.7 Swell compensation

The control algorithm for voltage swell is shown in Figure 3.11. The voltage swell is created at the main supply source.

Figure 3.11: Algorithm for voltage swell

# 4. Results and Discussion

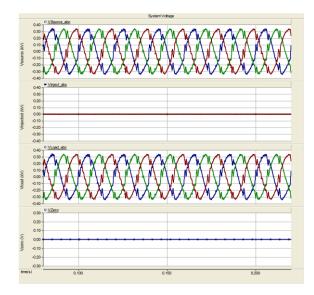

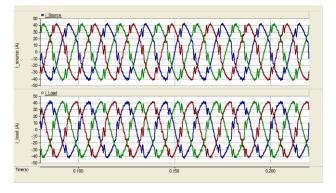

PSCAD/EMTDC was adapted to verify the effectiveness of the proposed control technique. The distribution system is rated at 400 Volts delivering a sensitive load of 29.5 kVA. The filter resistor, inductor and capacitor values have been determined for this application on the assumption that switching harmonics above 250 Hz are attenuated. Case 1: to analyze and evaluate the improvised control robustness against voltage harmonic distortion. Figure 4.1 shows simulation results of load current under distorted supply voltage condition. For distorted and uncompensated condition, 10.51 % of the fifth and 9.07 % of the seventh harmonics, respectively, 5.36 % of the eleventh and 8.37 % of the thirteenth harmonics, respectively, are subjected to the supply voltage, which results in THD of 12.06 %. Figure 4.2 shows simulation results of load voltage under distorted supply voltage condition.

Figure 4.1: Load current under distorted supply supply voltage condition.

Figure 4.2: Load voltage under distorted voltage condition.

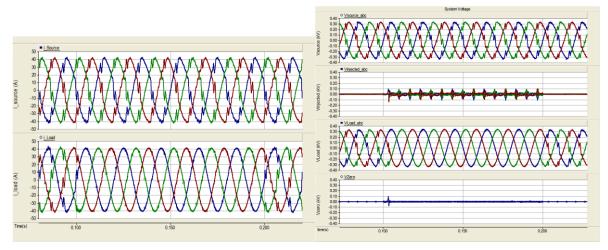

Figure 4.3 shows simulation results of load current after compensation. For undistorted condition, 1.19 % of the fifth and 0.71 % of the seventh harmonics, respectively, 0.82 % of the eleventh and 0.91 % of the thirteenth harmonics, respectively, are subjected to the supply voltage, and the THD of the voltage has been significantly reduced to 1.63 %. Figure 4.4 shows simulation results of load voltage after compensation.

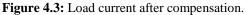

Figure 4.4: Load voltage after compensation.

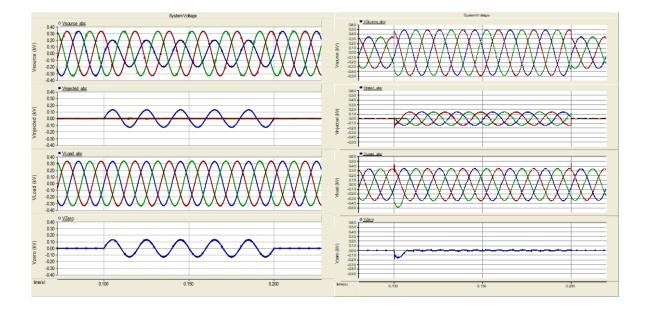

Case 2: to analyze and evaluate the improvised control robustness against voltage swell. The simulation started with the supply voltage swell is generated on phases abc as shown in Figure 4.5. As observed from this figure the amplitude of supply voltage is increased about 15 % from its nominal voltage rising to 500 Volts. The same figure shows the injected and the load voltage, respectively. The DVR reacts quickly to inject the appropriate voltage component (negative voltage magnitude) to correct the load voltage. As can be seen from the results, the load voltage is kept at the nominal value 340 Volts by the DVR. Case 3: A single line to ground fault is applied on phase a. The healthy phases show the same magnitude. The supply voltage on phase a dropped to 200 Volts which also affected the supply phase a voltage at the sensitive load downstream. For 100 ms, the DVR starts injecting the required compensating voltage, thus restoring the voltage at the sensitive load to its rated value of 340 Volts and is sinusoidal. The results confirm the improved transient performance of the DVR. The simulated result for a single line-to-ground fault with the injected voltage and voltage at the sensitive load is shown in Figure 4.6.

Figure 4.5: Swell mitigation by DVR

Figure 4.6: Single line to ground fault

Table 4.0 is the summary of voltage sag and restored voltage for single line to ground fault.

| Single line to ground fault |             |              |                  |  |  |

|-----------------------------|-------------|--------------|------------------|--|--|

| Phase                       | Voltage sag | Compensating | Restored voltage |  |  |

|                             |             | voltage      |                  |  |  |

| a                           | 200 V       | 140 V        | 340 V            |  |  |

| b                           | NIL         | NIL          | 340 V            |  |  |

| с                           | NIL         | NIL          | 340 V            |  |  |

Table 4.0: Summary of voltage sag and restored voltage

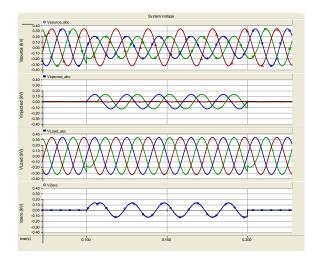

Case 4: A double line to ground fault is applied on phases a and b to ground. The healthy phase shows the same magnitude. The supply voltage on phases a and b dropped to 200 Volts which also affected the supply phases a and b voltage at the sensitive load downstream. For 100 ms, the DVR starts injecting the required compensating voltage, thus restoring the voltage at the sensitive load to its rated value of 340 Volts and is sinusoidal. The results confirm the improved transient performance of the DVR. The simulated result for a double line-to-ground fault with the injected voltage and voltage at the sensitive load is shown in Figure 4.7. Table 4.1 is the summary of voltage sag and restored voltage of each phase.

Figure 4.7: Double line to ground fault

Table 4.1: Summary of voltage sag and restored voltage

| Double line to ground fault |             |              |                  |  |  |

|-----------------------------|-------------|--------------|------------------|--|--|

| Phase                       | Voltage sag | Compensating | Restored voltage |  |  |

|                             |             | voltage      |                  |  |  |

| а                           | 200 V       | 140 V        | 340 V            |  |  |

| b                           | 200 V       | 140 V        | 340 V            |  |  |

| с                           | NIL         | NIL          | 340 V            |  |  |

| Description                                     | [13]          | [14]          | Current Study   |

|-------------------------------------------------|---------------|---------------|-----------------|

| Year                                            | 2012          | 2012          | 2020            |

| Operating voltage and frequency                 | 400 V 50 Hz   | 400 V 50 Hz   | 400 V 50 Hz     |

| Inverter type                                   | 3-level       | 3-level       | Cascade 7-level |

| RMS of the supply side voltage                  | 240 V         | 240 V         | 240 V           |

| RMS of the load side voltage after compensation | Not available | Not available | 240 V           |

| THD of the supply side voltage                  | Not available | Not available | 12.06 %         |

| THD of the load side voltage after compensation | 3.9 %         | 4.35 %        | 1.63 %          |

Table 4.2: The comparison of the related research and current investigation

# 5. Validation

A new methodology for voltage imperfection is proposed in this research. Mathematical and simulation results display the accuracy and applicability of the proposed methodology for the application. From the results it can be concluded the proposed DVR model is accurate for power quality improvements. A comparative analysis shows the THD level in the system is reduced from 12.06 % to 1.63 % compared to some classical controllers as shown in Table 4.2. The calculated output of the methodology accurately represents the voltage disturbances. The simulation results validate and justify that the proposed innovative synchronous rotating reference frame algorithm is a superior approach than the classical schemes.

## 6. Conclusion

The foremost research is the development of an improved innovative DVR model in PSCAD platform. An improved inverter topology for the DVR that will compensate the voltage swell, voltage sag and reduce the level of voltage harmonics. The DVR was developed with an innovative new improved control technique that can improve the transient and steady-state response and improve the injection capability for the mitigation of voltage swell / sag and suppression of voltage harmonics in the power distribution network. Improving the voltage injecting capability of the proposed DVR will increase the ride-through capability characteristics of the DVR both for the suppression of voltage harmonics as well as mitigation of short and deep voltage sags. The DVR has reduced the THD level at the sensitive load within the permissible limit. A new innovative Synchronous Rotating Reference Frame (SRRF) based control scheme was developed. Two dq/abc controllers incorporating a PLL were used. The PLL is for synchronization with the supply voltage. The other controller provides the feedback control loop for zero sequence unbalance fault. No PI controllers and 5<sup>th</sup> and 7<sup>th</sup> harmonics tuned passive filter banks were employed as in most of the literature. Thus, the new control scheme was able to detect the voltage imperfections fast and accurately. The accurate injection of the compensating voltage by the DVR as

a counter measure to minimize both the voltage sag and voltage harmonics is an innovative technique. The results showed a decrease in overshoot. The proposed vector control strategy conferred the DVR stable operation for the various voltage discrepancies. The DVRs new innovative control scheme was able to operate both in the distorted and unbalanced supply conditions. Simulation results have proved the effectiveness of the DVR under various fault conditions in a distribution network supplying the sensitive loads. The simulation results confirm and justify that the proposed innovative synchronous rotating reference frame algorithm is a superior approach than the classical schemes.

## 7. Recommendations

The cost of the DVR may be significantly reduced by the reduction of the energy storage element and size and efficient utilization of the energy. This is an area of challenge and the research may focus on the various alternatives such as fuel cell, super-capacitors, motor-generator flywheel etc. Alternative control strategies on the switching and power management to improve the efficiency and utilization could be explored. A switch-mode power supply or dc/dc converter may be added, to regulate the dc voltage of the energy storage element. Another area of research is by applying a filter-less DVR, especially between the inverter output and the secondary of the injection transformer. This will be very important when inverters are operating at very high switching frequencies. At high frequencies, the injection transformer leakage reactance can suppress the high frequency harmonics. Operating at high frequencies improves the efficiency of the inverter but at the same time increases the losses due to switching.

## References

- Kannan Karthik and J.E. Quaicoe, "Voltage Compensation and Harmonic Suppression using Series Active and Shunt Passive Filters", Electrical and Computer Engineering, Canadian Conference, Vol. 1. pp. 582-586, 2000.

- [2]. Hideaki Fujita and Hirofumi Akagi, "A Practical Approach to Harmonic Compensation in Power System- Series Connection of Passive and Active Filters", IEEE Transactions on Industry Applications, Vol. 27, Issue N0.6, November/December 1991.

- [3]. Bhim Singh, "Power Quality: Problems and Mitigation Techniques", John Wiley and Sons Limited, 2015.

- [4]. Zhongdong Yin and Lixia Zhou, "A Novel Harmonics Injecting Approach on Over Saturation Suppression of DVR Series Injection Transformer", IEEE, Power Engineering Conference, pp. 1-5, 29 Nov 2005.

- [5]. Steven M. Hietpas, "Automatic Voltage Regulator Using an AC Voltage-Voltage Converter", IEEE Transactions on Industry Applications, Vol. 36, No.1, pp.33-38, January/February 2000.

- [6]. Sunil Kumar Gupta, "Study of Major Issues and Their Impact on DVR System Performance", International Journal of Computer and Electrical Engineering, Vol. 2, No.1, pp. 105-110, February 2010.

- [7]. A.Venkatakrishna, "Phase Shifted and Level Shifted PWM Based Cascaded Multilevel Inverter Fed Induction Motor Drive", International Journal of Current Engineering and Technology, Vol.4, No.1,

pp.350-354, February 2014.

- [8]. N.H. Woodley, "Field experience with Dynamic Voltage Restorer" Power Engineering Society Winter Meeting, vol. 3, pp. 1323-1328, IEEE, 2000.

- [9]. Sasitharan S, "Rating and Design Issues of DVR Injection Transformer", IEEE, Applied Power Electronic Conference (APEC), pp.449-455, 24-28 Feb. 2008.

- [10]. Mahinda Vilathgamuwa and S.S.Choi, "Performance Improvement of the Dynamic Voltage Restorer with Closed-loop Load Voltage and Current-Mode Control", IEEE Transaction on Power Electronic, Vol.17, No.5, pp. 824-834, September 2002.

- [11]. H. Tiwari, "DC Energy Storage Schemes for DVR Voltage Sag Mitigation System," International Journal of Computer Theory and Engineering, vol. 2, no. 3, pp. 313-318, June 2010.

- [12]. Suresh Kumar, "Mitigation of Lower order Harmonics in a Grid connected Three Phase PV Inverter", International Research Journal of Engineering and Technology (IRJET), Vol 02, pp. 1036-1046, Aug 2015.

- [13]. AlirezaJavadi, "A Novel Transformerless Hybrid Series Active Filter", IEEE Industrial Electronics Society, pp.5312- 317, 25-28 Oct. 2012.

- [14]. M. A. Mulla, "A Simplified Control Strategy for Series Hybrid Active Power Filter that CompensateVoltage Sag, Swell, Unbalance and Harmonics" IEEE, pp. 1-6, 6-8 Dec.2012.

## 8. Biography

K Chandrasekaran is an Assistant Professor in the department of Industrial engineering at University Tunku Abdul Rahman (UTAR) Kampar, Perak. He holds a Master of Science in Electrical and Electronics Engineering from University Technology Petronas (UTP) and PhD in Engineering from University Tenaga Nasional (UNITEN). He is a Competent Electrical Engineer. Has published in journal and conference papers. His research interests include Power Electronics, FACTS, Power Systems, and Filters.